近期,电子设计自动化(EDA)领域顶级会议Design Automation Conference(DAC 2026)揭晓论文录用榜单,学院牛丹老师团队在卡脖子的芯粒异构集成和高带宽内存(HBM)设计仿真加速中取得新的进展,3篇论文被该EDA领域顶级国际会议收录。相关工作得到国家级青年人才项目、国家重点研发计划项目、国自然重点和面上项目、江苏省优青等项目支持。

DAC会议被誉为EDA界的“奥斯卡”,同时也是EDA领域唯一CCF-A类会议,由美国电子协会(ElectronicDesignAutomationConsortium)主办,目前已经举办63届,每年提供近300多场的技术演讲,是EDA领域规模宏大、影响深远、历史悠久的顶级会议。部分论文介绍如下:

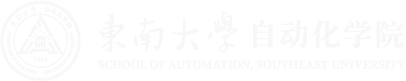

论文1:模块化和可重构的芯粒异构集成热模型构建和仿真算法

在后摩尔时代,热管理对于芯粒异构集成电路的可靠性至关重要。设计过程需要在不同的功率分布、冷却条件和结构配置下进行数百次热仿真。传统的基于有限元法(FEM)和紧凑热模型(CTM)的方法缺乏灵活性,无法进行高效的多场景评估,并且在对具有跨尺度互连的复杂垂直堆叠进行建模时会产生过高的计算成本。我们提出了LegoTherm,一个模块化的热建模框架,它将基于芯粒的系统分解为可重用的降阶组件。该框架利用异构集成固有的分层结构,通过模块化离散化构建高保真度的三维网格,捕捉微互连的细节,然后通过聚合热耦合端口生成降阶模块。这种方法既能保持关键热点的精度,又能针对不同的设计场景快速重新组装。在工业级2.5D和3D封装基准测试中,LegoTherm的速度比商业COMSOL最高提升10.39倍,同时保持平均相对误差低于0.40%。该框架将芯粒热设计迭代周期从数周缩短至半天,解决了芯粒热设计的一个关键瓶颈。

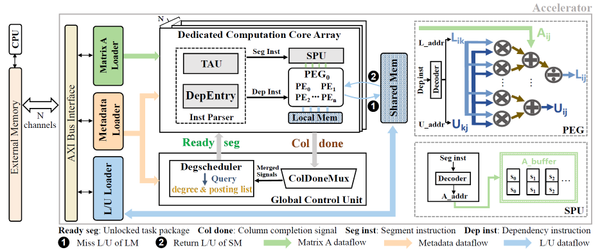

论文2:基于异步任务触发的HBM 高性能稀疏 LU 分解加速架构

稀疏LU分解作为科学计算、电路仿真及线性电路系统分析等领域的核心计算算子,其执行效率直接影响着大规模复杂系统的仿真速度。虽然集成高带宽内存(HBM)的 FPGA 为处理此类内存密集型任务提供了极高的并发访问潜力,但在应对稀疏计算中固有且不规则的数据依赖关系时,传统硬件架构仍面临严峻挑战。现有的加速方案往往受限于刚性的层级同步机制,导致显著的同步开销与计算资源闲置,且中心化调度器在处理大规模并行任务时极易成为性能瓶颈。为了在保持计算精度的同时突破这些性能限制,我们提出了 SALUT,一种新颖的基于异步任务触发的HBM FPGA稀疏LU分解加速框架。该方法的核心在于开发了一种异步任务激活机制,通过预编译技术将复杂的运行时数据依赖解析转化为细粒度的段级依赖管理,从而消除了传统列级同步中的冗余等待过程。在硬件架构层面,SALUT 实现了任务激活与依赖解析的深度解耦,配合局部性感知双队列负载均衡策略,在确保高缓存命中率的同时最大化了处理单元的利用率。算法在 15 个真实稀疏矩阵测试中展现了卓越性能,实现了相较于英伟达NVIDIA尖端库 cuDSS(基于 RTX A6000 GPU)高达 4.0 倍的吞吐量提升和 6.5 倍的能效比提升,即便与 Tesla V100 GPU 相比,其性能和能效也分别达到 3.7 倍和 4.7 倍。所提出的 SALUT 模型通过异步流式调度显著降低了非规则计算中的处理延迟,实现了后续大规模系统仿真速度的质变。

作为支撑数千亿半导体产业“皇冠上的明珠”和制约后摩尔时代半导体产业发展的关键瓶颈之一,EDA工具已成为全球半导体产业竞争日益激烈下的必争之地,也将是国家发展战略的重中之重。在EDA中,快速准确的大规模电路仿真技术将是支撑后摩尔时代模拟及混合集成电路智能、敏捷设计的关键核心。近年来,学院牛丹老师团队聚焦人工智能与大规模集成电路设计及仿真加速交叉方向提出了一系列优化策略,在DAC、ICCAD、DATE、IEEE TCAD、IEEE TC、CVPR、AAAI、ICCV等EDA或人工智能领域的顶级国际会议、期刊上发表论文30余篇。在应用方面,团队与多家国内头部EDA公司开展广泛产学研合作,将算法研究成果在工业界应用落地,在大规模集成电路电路生成、直流分析、瞬态分析、芯粒电热仿真等一系列芯片设计验证重要环节中为客户提供核心算法支撑。